芯片设计“花招”已耍完?无指令集架构颠覆旧套路

日前,英伟达在GTC大会上发布了最新一代GPU H100,采用台积电4nm工艺,集成了800亿个晶体管。3月初,苹果发布了M1 Ultra芯片,更是集成了高达1140亿个晶体管。显然,头部厂商都在推进现有芯片设计和制造技术的极限,但问题是,当这些“花招”用完后怎么办?

在面向AI负载的新锐芯片创业企业里,SambaNova和 Tenstorrent 都足够引人注目,他们都可以视作为数据流架构专门设计的软硬件系统。 据公开资料,他们都十分强调编译器软件的重要性,虽然硬件是重配置的,但重配置方案却是编译器完成的,其中最核心的问题是解决placement和routing问题,看上去他们都解决得不错。

其实,在这两家企业之前已经有“先烈”公司Wave Computing走过这条路,但不幸没有走通。其实所有这些努力背后可以追溯到VLIW。Wave Computing破产之后,CEO Peter Foley东山再起,在Ascenium公司继续向VLIW架构冲锋,看上去他信心满满,的确该到通关的境地了。

作者|Timothy Prickett Morgan

翻译|刘晓祯、张雨珊、胡燕君、徐晨阳、沈佳丽、周亚坤

在任何架构中总有一些必不可少的、基础性的且毋庸置疑的功能。直到某个聪明的架构设计师出现,才告诉我们情况并非如此。建筑物和桥梁是这样,系统及其处理器同样也是如此。这就是为什么我们用同一个词“架构设计师”来描述设计宏观和微观结构的人。

Ascenium公司的联合创始人兼CEO Peter Foley就是这样一位架构师,该公司刚刚在2021年A轮融资中筹集到1600万美元。Foley和他带领的Ascenium团队想摒弃现代CPU中的很多架构,从头开始开发Foley所谓的由软件定义的、可连续重配置的处理器。Foley说,之所以有必要拆解处理器,再以一种全然不同的新方式构建它,是因为当前CPU的架构技巧已经用完了。

先介绍下Foley,再谈Ascenium公司正在开发的Aptos处理器架构,以及它将如何撼动CPU市场。

Foley涉猎广泛、见识极深,这使他走到了今天这一步。他先在莱斯大学获得了电子工程学士学位,之后在加州大学伯克利分校获得硕士学位。在伯克利时,Foley与David Patterson(Google Brain团队成员)和Alvin Despain(美国电气工程师,曾任Acorn Technologies联合创始人兼CTO)一起用Smalltalk语言做RISC(SOAR)芯片项目。

毕业后,Foley加入苹果公司开始研发Mac和Mac II电脑中的各种芯片,1987年,他成为研发“牛顿个人数字助理机(PDA)”的四个原始成员之一。PDA是iPad平板电脑的前身,但当时还没人知道。值得一提的是,Foley负责开发用于PAD的“Hobbit”处理器。离开苹果后,他加入了第三方GPU供应商SuperMac,之后在Chromatic Research公司开发可编程的VLIW和SIMD媒体处理加速器。

Foley在风投公司Benchmark Capital做了一段时间的入驻企业家,然后创立了nBand Communications,并创造了软件定义的宽带无线广播(类似于WiMAX,而不是5G,说实话,在多数地方这更像是4.1G)。

然后,他在Predicant Biosciences公司做了近四年的工程副总裁,该公司开发了用于扫描血液蛋白中是否有癌症的诊断设备。之后,他在风投公司Tallwood做了近四年的驻校执行官。

经历这一切之后,特别是在2009年12月,Foley意识到加速计算前景黯淡,就成立了人工智能芯片创业公司Wave Computing并担任CEO。值得注意的是,Foley离开了Wave Computing,数年间,这家公司通过复杂的交易把技术授权给中国企业,还收购了MIPS芯片公司。而MIPS芯片公司自从硅图公司(SGI, Silicon Graphics)十几年前将其分离出来之后,就在不停被转手。最后,Wave Computing在2020年4月不得不申请破产重组。

准确来说,Foley是在2016年6月离开的Wave Computing,并开始经营自己的咨询业务,直到2019年6月,他以CEO的身份加入于2018年3月成立的Ascenium公司。

Ascenium公司获得了900万美元的天使轮融资和1600万美元的A轮融资。投资方Stavanger Ventures AS是一家风投公司,由挪威企业家Espen Fjogstad运营,他创立的公司曾被eBay和谷歌收购,还有多家公司在奥斯陆证券交易所上市;其中有几家公司是做储层建模(reservoir modeling)的,期间在北海石油热潮中派上了用场。自20世纪70年代末起,北海石油热潮为英国和挪威的经济注入了新的活力(油价在升高,技术也在发展,而海上钻探石油是经济型的)。

据了解,Ascenium最早成立于2005年之前,当时它的创始人兼CTO Robert Mykland在Hot Chips会议上做了一个演讲

( https://llvm.org/ProjectsWithLLVM/Ascenium.pdf )。该公司已获得九项专利,在诉讼频发的半导体领域,这些专利很有用。Ascenium目前的实体公司成立于2019年6月,致力于充分利用和发展Foley、Oyvind Harboe和Tore Bastiansen的研究成果。

“牛顿个人数字助理机(PDA)”当时领先于时代,依据摩尔定律,在芯片和网络的发展迎头赶上后,我们才真正有了PDA。类似地,也许我们必须等到摩尔定律终结后,才能去思考Robert Mykland(Ascenium的CTO)早在16年前就提倡的观点。

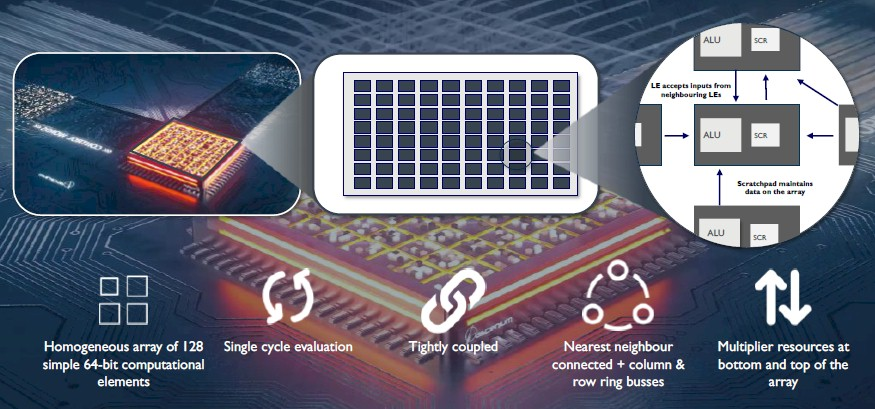

在了解背景信息后,我们与Foley聊了Ascenium正在研发的处理器,它并没有如我们熟知的那样有一个指令集,而是试图通过Aptos处理器重新定义软件编译器和底层硬件之间的接口。Aptos处理器是一个由64位计算单元组成的可编程阵列。下面是一个大概的结构图,有点模糊,因为Ascenium目前还比较神秘。

以下是与Foley的对话。

1

摒弃旧传统的“无指令集架构”

Timothy Prickett Morgan: 我好像看到的是一个没有指令集架构的处理器。我看了两遍,然后摇摇头说,这是个什么东西?它成功地引起了我的注意。

Peter Foley: 我之前在Tallwood时,老板Dado Banatao说过,如今市场巨大、尚未复苏,对于创新来讲,时机已经成熟。我们的使命就是,带着完全不同的新事物进入这个巨大的市场。

我们认为它必须是完全不同的架构,如果你一直在同一个沙盒里遵守同一套规则——就是说指令集架构,你得有串行指令流进入带有深层管道的乱序发射处理器(out-of-order issue machine)——我就不细说了,如果你遵守这些规则,就赢不了。看看那些ARM牺牲品:Calxeda,Cavium,Broadcom等等。

TPM: 确实有很多牺牲品,价值几十亿美元的牺牲品。

Peter Foley: 高通公 司已经尝试过两次,他们仍在努力。在单核、单线程的SPECint上击败Intel很困难,这才是人们真正关心的问题。

TPM: AMD正在做这件事。

Peter Foley: 是的,但AMD仍然用的是X86架构,而且他们有许可证。AMD现在可以说是在某种程度上打败了Intel,但这很大程度上与Intel在晶圆厂选择的失误有关,而AMD使用的是台积电(TSMC),因此他们在一段时间内有节点优势。

TPM: 我最近写了一篇文章,还没发表,我说AMD史上最好的消息就是GlobalFoundries(半导体晶圆代工厂商)搞砸了14纳米技术,但IBM把自己的微电子部门卖给了GlobalFoundries,这起到了作用,然后10纳米确实搞砸了。因为在那之后,AMD不得不采用台积电的7纳米制程,同时Intel在10纳米上遇到了大问题。AMD总能设计出优质的芯片,但Intel的晶圆代工问题影响太大了。

Peter Foley: 你说得对。架构微调,再投入几十亿个晶体管,这些都是次要的。然而,摩尔定律和Dennard缩放比例定律并不匹配,因为这些架构非常复杂,必须投入几十亿个晶体管,才能提高5%、10%、20%的性能。问题是这样一来温度就太高了,你要么调小时钟,要么关掉部分模具——然后就有了暗硅问题。

TPM: 我一直在说把时钟调小,让内存和CPU回到接近相位的状态,因为你在大部分时间都只是在旋转时钟来等待。所以还不如慢一点,不要等待。为了在GPU上运行,我们必须并行化代码,所以要让CPU看起来像GPU,并通过这种方式提高其处理能力。

Peter Foley: 英伟达的Ampere GPU也有这个问题。它们发热比较厉害,即使时钟较慢,也有400瓦,这意味着Ampere不能在PCI板上使用,而要重新设计,使其适合300瓦的PCI-Express。

TPM: 所以,我认为这为Ascenium试图做的事情奠定了基础。

Peter Foley: 我们正在做的事情将是非常不同的。这个想法是让我们重新定义编译器和硬件之间的划分(partitioning),它建立在50年前使用ISA的IBM大型机以及后来的RISC机器上。

当时,你有一个三阶段或五阶段的流水线,编译器能处理的东西比较有限,因为你没有太多的马力。但这在当时似乎是一个很好的分工了。问题是,这种API划分已经变得非常陈旧,50年后的今天,随着计算能力的提高,以及我提到的Dennard缩放比例定律和将晶体管放在一个乱序架构中的问题,这种划分已经不能真正发挥作用。

现在是重新思考的时候了,我们应该摒弃与旧ISA相关的所有内容 :深层流水线、乱序、重新排序、重命名、转发、运行时分支预测,把这些东西通通丢掉。

TPM: 那还剩下什么呢?你刚刚说要丢掉的东西,基本上就是我所理解的一切了。

Peter Foley: 我们现在有一些关键的推动因素了,一个是现在有大量的马力用于编译器。所以你可以让更复杂的编译器做更多的工作,因为有足够的马力来做。

另一个驱动因素是,如果你打算使用一种基于阵列的方法,直接由编译器进行极细粒度的控制的话,这就有点像你把一个容量庞大的微码放到基于阵列的机器里,那么你使用的编译器通常是一维的。会生成一串指令流,然后你会把指令发给硬件,硬件必须提取所有的并行,完成所有事。与此相反,我们说要让编译器完成大量的工作,深入地了解整个程序,并且进行更加复杂的优化。现在的编译器是5D编译器,它需要做2D布局、2D布线以及调度,所以还有更多工作要做。

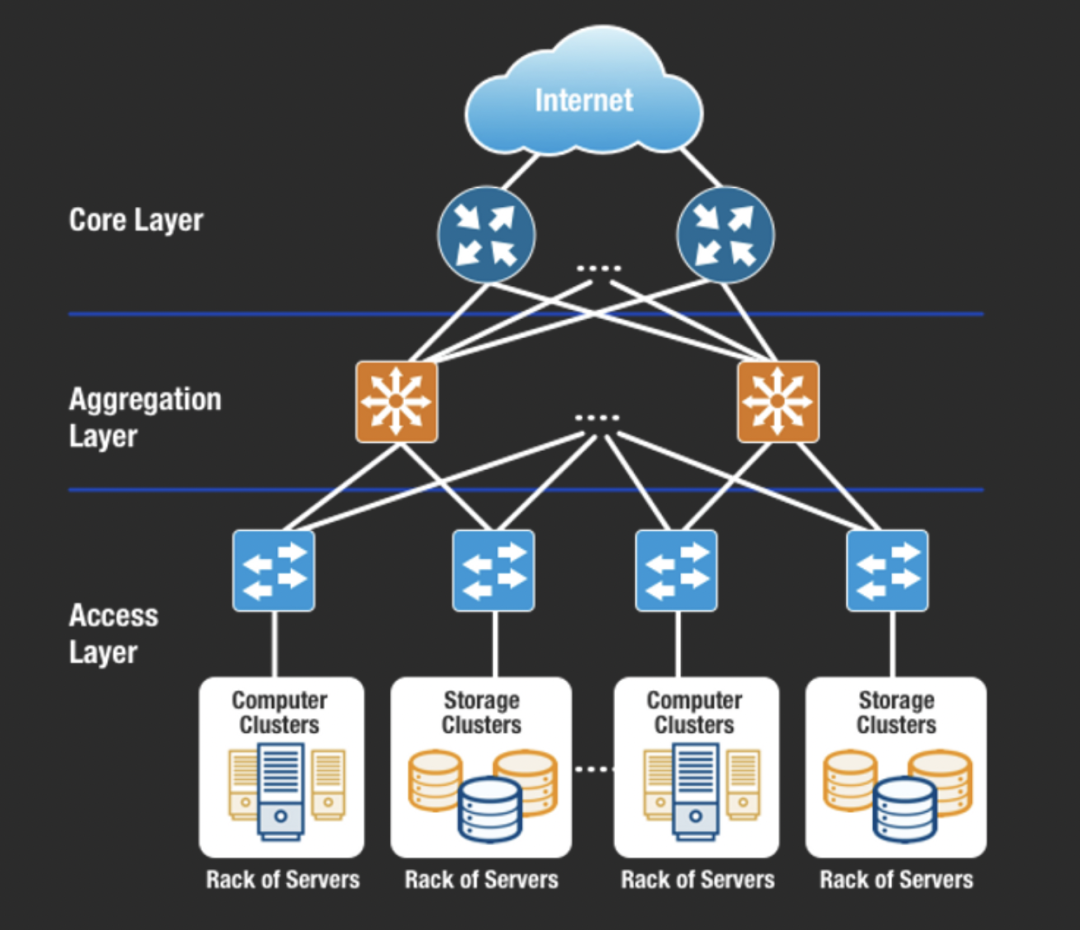

因为我们瞄准的市场是数据中心,所以可以一直重新编译。我们可以花15分钟到半个小时进行编译,然后在数据中心运行1000万次,并收获能耗回报。从对能耗的全面关注来看,这种计算方式也发生了变化。

因此,值得一试的是能否花更多时间在一个非常复杂的2D计算阵列上,这个阵列由一个有巨大容量微码的编译器直接控制。如果能节省5%或10%的功耗,这就是值得的。如果你能做到的话,超大规模企业将竭力邀请你接入他们的数据中心。

说到Ascenium的Aptos处理器和我们的办法,其实还有一个关键的驱动因素。我一直都在深究这个问题,这也是我为这家公司所做的一点贡献。我意识到了这一点,并且认为这的确会对Ascenium当前的工作产生一定的影响。

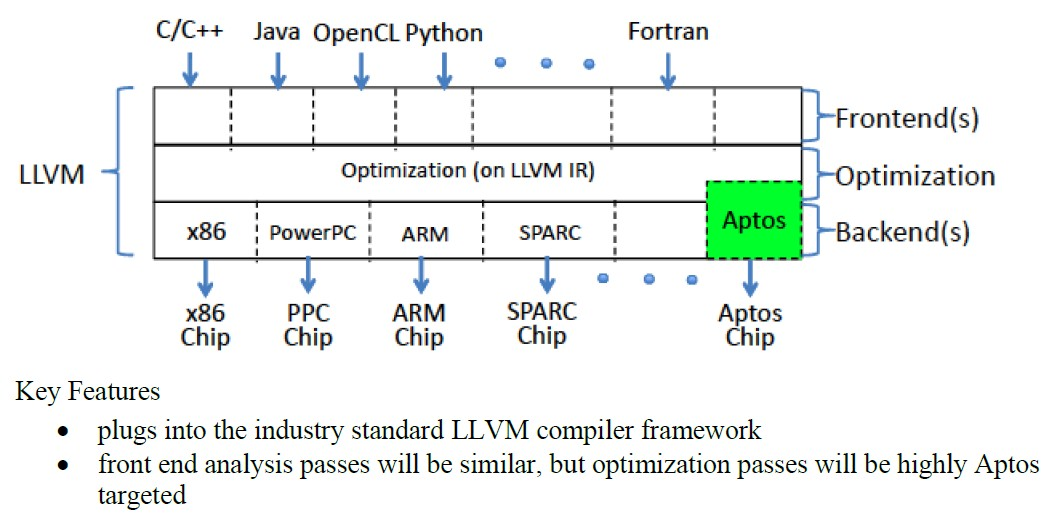

一家名为Tabula的公司也遇到了类似的问题。他们在软件工作时遇到了真正的难题,结果还是在他们做第二次还是第三次尝试时引入了约束求解器,这才解决。Tabula使用基于SAT求解器的方法来编译后端。我们在Wave Computing时也采取了同样的办法,后来我又把这项技术带到了Ascenium。

我们有一个标准的LLVM编译器基础设施,外加一个新的LLVM后端,主要面向适合约束求解器的硬件。它就像一个黑匣子,如果你有一个非常简单的规则架构,都可以在一组逻辑方程中完整地描述行为,无论是在时间还是物理上,那么我们的SAT求解器可以分析、解读它,并给出数学上的最佳证明结果。

这是很难被超越的。永远不能在一个复杂、异构、无序的体系结构上使用约束求解器。算了吧,那是在浪费时间。但在我们的场景,这是可行的。

当讨论整个程序时,SAT求解器方法的数学最佳证明结果是言过其实的。从数学上,它对于代码块来说是最佳的。但对于整个程序来说,计算起来却有些棘手。

这些代码块就不得不拼接在一起。所以SAT求解器窗口贯穿整个代码,将编译后的窗口拼接在一起(这会降低效率)。因此,公司的诀窍之一就是知道如何最优地分割、编译和拼接SAT编译过的程序块。

我们的想法是使芯片的架构尽可能简单,这样把它安装到SAT求解器上后就会得到令人惊讶的、最佳的5D解决方案。 这就是一场赌注:除了要跳出X86和ARM沙盒,还得有一个IP清除方法,这很重要。这又是另一个问题了:如果你试图和这些CPU架构展开角逐的话,就会撞上巨大的IP墙。一旦你开始对他们构成威胁,他们就会马上起诉你。这就是生意,对吧?

2

通过架构简化释放性能

TPM: 所以这是一种做到极致的RISC吗?

Peter Foley: 没错。而且我就是做这个出身的。很久之前,我在伯克利的时候,在一个芯片研究团队跟David Patterson一起研究Smalltalk语言。我的整个职业生涯几乎都在研究处理器,而且绝大部分都是RISC处理器。

TPM: 我觉得这可以称得上是NISC(无指令集计算)了,因为是把RISC(精简指令集计算)做到了极致,对吧。

Peter Foley: 哈哈,没错!但说实话,约束求解器现在是个热门话题,可以说席卷了整个EDA(电子设计自动化)行业。本质上,我们现在做的事情其实更属于EDA问题,而不是传统的编译问题。有点像把一个完整的Xilinx或Altera FPGA后端结合到编译器里,因为它们的很多功能和FPGA查找表结构中的放置、布线、调度是差不多的。我们做的事情和这个很像,只是我们把目标放在通用计算引擎。约束求解器现在正在很多其他地方运用,但把它用在通用计算上,是我们的创举。目前我们正在努力申请知识产权和专利等,希望取得先发优势。

TPM: 所以这有点像是FPGA数据流引擎和CPU之间的东西,能不能这么理解?

Peter Foley: 可以这样说。不过我们这个是通用处理器,并不像FPGA那样用查找表结构来模拟硬件的。

还有一点挺有意思的,在X86指令流里,至少50%的指令都是和数据搬运相关的移动指令,而实际运算的指令,比如加减乘之类的,大概只占20%。但在我们的处理器中,编译器可以用同一套控制字密切控制一切,也就是说,数据搬运、运算、设置文本流方向、布线等等,都可以由编译器通过阵列中的同一控制字同时控制。所以,我们的产品中不存在序列化,当指令汇入只执行搬运的架构时也不会出现阿姆达尔定律带来的缺点,因为一切都由编译器完成了。

编译器需要同时跟踪很多东西。但在典型的乱序机器中,有大批量的重命名正在执行,这是非常复杂的,需要阵列中有充足的资源来高效执行这种超大容量的分布式重命名。因此我们采用了分布式内存,并通过大量复用来减少进入典型寄存器堆(Register File)的流量,这样一来就可以实现简化。可以说,我们基本上没有处理流程,所以分支阴影(branch shadow)特别短。这就是我们的独特之处。

TPM: 所以可以说,惠普和英特尔联合开发了EPIC(显式并行指令计算),然后嫁接到一个类似X86,但又不如它的东西上,就做出了Itanium(安腾)。而现在你们摒弃了惠普和英特尔的成果,只保留了EPIC的部分……

Peter Foley: 我猜你下一句可能会问,这是真的吗?

TPM: 也不全是。你要理解一下我们,所有的AI初创公司来到我们这儿,我和Nicole(TPM的搭档)都会开他们的玩笑,这些公司的硬件都做得不错,然后侃侃而谈他们开发出来的编译器有多么厉害。他们总是先铺垫介绍一番,然后说“我们的编译器可以把这些问题统统解决”。但你所说的编译器是我目前听过最神奇的。所以,如果我持怀疑态度的话,那可能是因为我也许还不太了解……

Peter Foley: 我们的投资者之所以愿意投资A轮,帮助公司进一步发展,其中一个原因是我们已经证明了自己能够在5到10分钟内编译出70万行代码,并在FPGA原型上成功运行。这正是我们这个架构让人眼前一亮的地方:它非常简单,以至于你可以在FPGA上制作原型。

TPM: 更准确地说,这难道不就是把四块板组合起来模拟一块小型芯片吗?然后每块板上都配备了八个FPGA,还是最贵的那种。

Peter Foley: 当然不是。不同于Paladium仿真器,我们用的只是一块中档的FPGA板,不然可就负担不起了。

我们可以运行700,000行代码,其中包括SPEC中用到的C语言标准库。我们将这些代码编译好,并在我们的FPGA测试平台上运行。FPGA测试平台并不是完整的架构,它只是整体架构的一部分,并且得出功能正确的结果。我们有大量的符号调试器和其他一些基础设施来辅助此类操作。

TPM: 当它成为产品时会是什么样子呢,而你又将如何推销它?

Peter Foley: 我们正尝试在两个最重要的指标上取胜。第一个是SPECint性能,我们一般通过指令/时钟(IPC)来衡量,但它其实不是一个很好的衡量标准。但我们有一个指标,即我们的每个控制字中执行的工作就相当于 X86指令。若从结果和优化的角度来评估编译器质量的话,下一步我们计划在IPCW、指令/控制字、以及IPC等值这些方面做相应调整。这一步对于超大规模的处理器来说至关重要。

TPM: 你们这完全是在赌一把。

Peter Foley: 另一个指标则是功耗。我们的想法是要把这两个指标都拿下,并且对此胜券在握。为了降低功耗,我们去掉了所有的晶体管。

TPM: 所以,你看了一下需要拿掉多少个晶体管才行,对吗?

Peter Foley: 很少,也就比X86少很多。

TPM: 大概是 一个数量级还是三倍?

Peter Foley: 应该是一个数量级。目前也还没有定论,所以我暂不清楚详细的数字。我们花这笔钱就是为了弄清这件事。我们会将微架构具体化并且敲定下来,然后构建一些试验硅(trial silicon),并得到5纳米工具,或者其他我们所需的东西,然后去构建这个微架构并进行布局。

这是构建处理器的其中一步,要做的就是处理所有的几何图形。这一步是为了解决空间延迟和距离限制。布局决定了许多因素,这些因素又会进而影响微架构。因此,我们必须解决好这些问题,同时还要留意其他问题。一旦我们开始深入研究这些问题,就能更加自信地告诉你那个数字究竟是多少。

TPM: 所以,如果要我来总结一下Aptos架构的话,那就是降低功耗、优化性能——但你却并不需要降价。

Peter Foley: 是的,没错。这样我们就不必花大价钱使用ARM架构了。

(本文已获取编译授权,原文:

https://www.nextplatform.com/2021/07/12/gutting-decades-of-architecture-to-build-a-new-kind-of-processor/)

其他人都在看

OneFlow v0.7.0 最新版本已发布,欢迎下载体验:https://github.com/Oneflow-Inc/oneflow

本文分享自微信公众号 - OneFlow(OneFlowTechnology)。

如有侵权,请联系 support@oschina.cn 删除。

本文参与“OSC源创计划”,欢迎正在阅读的你也加入,一起分享。

|

- 上一条: 与吴恩达创办Coursera后,她一头扎进数字生物学 2022-04-01

- 下一条: 摇滚开源人CC:热爱足球音乐,亦是工业互联网生态构建者! 2022-04-01

- OpenHarmony LiteOS C-SKY指令集移植指北 2021-11-10

- 怎么提高自己的系统架构水平 2021-07-21

- 英特尔开放 x86?事情恐怕没这么简单…… 2022-03-17

- LLVM之父Chris Lattner:编译器的黄金时代 2022-04-22

- “炫技”还是“真硬核”,OpenPPL 实测阿里「倚天 710」芯片 2022-05-10